元件,它可提供三种输出状态:高电平、低电平和高阻态。这种电路在实现数字系统之间的连接和数据传输时起着至关重要的作用。

TTL三态门输出电路的核心功能是在正常逻辑电平输出(高电平和低电平)之外,还能进入一个高阻态,即输出端相当于断开的状态,不对外部电路产生一定的影响。这种特性使得TTL三态门在多路复用器、数据总线和可编程逻辑设备中得到了广泛应用。

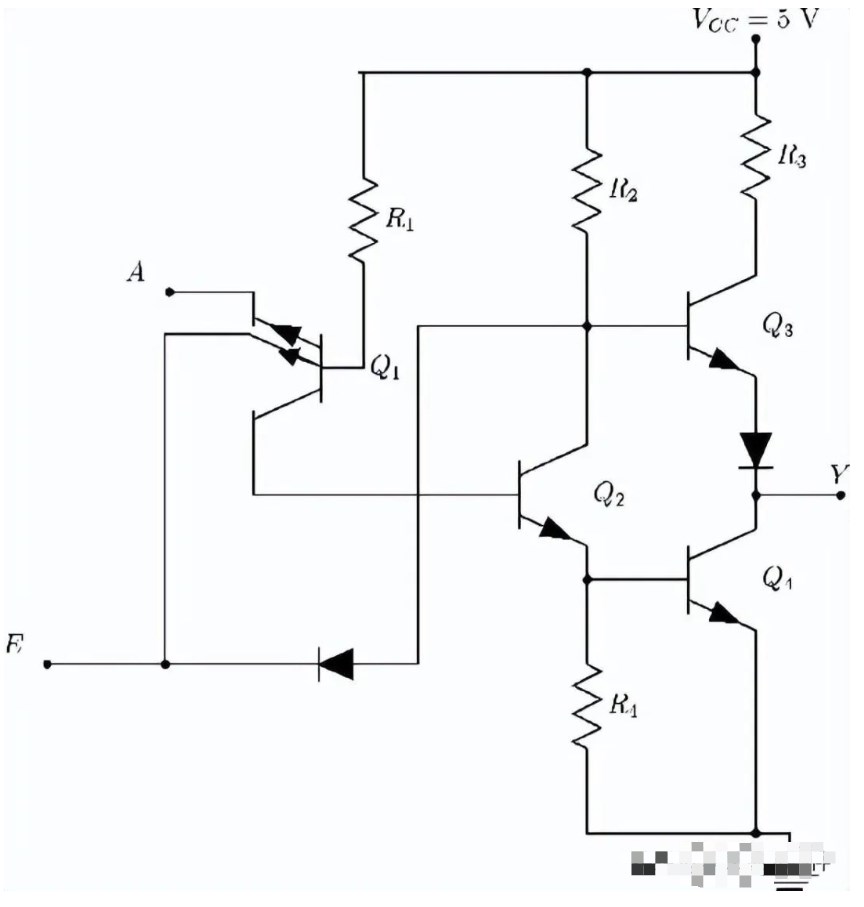

在分析TTL三态门输出电路的工作原理时,我们第一步需要了解其内部结构的组成。电路通常由一个标准的TTL逻辑门(如与门、或门等)和一个三态控制晶体管组成。这个控制晶体管的作用是切换输出端的状态:当控制信号为高电平时,晶体管导通,逻辑门的输出通过晶体管传送到输出端;当控制信号为低电平时,晶体管截止,输出端进入高阻态。

在这种输出配置下操作晶体管时,能够得到高阻抗。三种输出状态是:高、低和**高阻抗。

三态逻辑电路利用图腾柱排列的高速运行,同时允许输出进行线与运算(连接在一起)。Hi-Z 状态是图腾柱排列中的两个晶体管都关闭的状态,因此输出端对地和 V CC为高阻抗。换句话说,输出是一个开路或浮动终端,既不是低电平也不是高电平。实际上,输出端并不是完全开路,而是相对于地和 V CC具有几 MΩ 或更高的高电阻。

上图显示了三态逆变器的电路,该电路有两个输入:A 是正常逻辑输入,F 是能够产生 Hi-Z 状态的启用输入。

当 F = 0 时,无论逻辑输入 A 的状态如何,电路都会进入其高阻抗状态。F 处的低电平正向偏置晶体管 Q 1 的发射极-基极结,并使电阻R1 的电流从晶体管Q分流2使 Q 2关断,从而使晶体管 Q 4关断。E 处的低电平还正向偏置二极管D 2以从晶体管 Q 3的基极分流电流,因此 Q 3也关闭。由于两个图腾柱晶体管都处于截止状态,因此输出端绝大多数都是开路。

具体的可以看如下线 时,电路作为正常逆变器运行,因为 F 处的高输入对晶体管 Q 1或二极管 D 2没有影响。在此启用条件下,输出只是逻辑输入的反相。

:TTL三态门的传播延迟大约为10毫秒,这使得它们在工作速度上优于DTL(二极管-晶体管逻辑)和RTL(电阻-晶体管逻辑)器件。

:与早期的DTL和RTL逻辑器件相比,TTL三态门在功耗方面有所降低,这对于提高电路的效率和减少能源消耗是非常有利的。

:TTL三态门的生产所带来的成本相比来说较低,这使得它们在成本敏感的应用领域中更具吸引力。

:TTL三态门提供更好的扇出能力,即能够驱动更多的负载设备,这在需要连接多个设备的场合中非常有用。

:TTL三态门能够在噪声环境下可靠运行,这对于保证电路的稳定性和可靠性是很重要的。

:由于三态门具有高阻态的输出状态,能够最终靠合理的安排上班时间,将多个三态门的输出挂接在一根数据总线上,这种输出端并联的连接方式极大地提高了

输出驱动能力:TTL三态门的输出驱动能力是有限的,因此在设计时需要考虑到负载的大小。如果负载过重,有几率会使输出电平不稳定或者电路损坏。

输入电容:由于TTL三态门的输入端存在电容效应,当多个三态门并联在同一条总线上时,需要仔细考虑总线上的总电容对电路性能的影响。过大的电容有几率会使信号传输延迟增加,影响系统的速度和稳定性。

开关速度:TTL三态门的开关速度受到晶体管响应时间的限制。在需要高速切换的应用中,在大多数情况下要优化晶体管的选择和电路布局以提高效率。

电源电压:TTL三态门的工作电源通常为5V,但在不同的应用中在大多数情况下要不同的电源电压。因此,电路设计应当兼容不同电源电压的需求。

热稳定性:由于TTL三态门在工作时会产生热量,特别是在高负载电流下,因此就需要考虑电路的耐热性。这可能涉及到选择正真适合的散热器、使用温度补偿技术等措施。

端连接在同一条导线上,将这些与非门上的数据(状态)用同一条导线输送出去

能力?现在有几个疑问:1,他是怎么提高驱动能力的?我看244的手册,内部原理

inout Key_inout;wire Key_input;//输入reg Key_output;//

管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件.在硬件 上,可用OC

【嵌入式SD NAND】基于FATFS/Littlefs文件系统的日志框架实现

【原创】收藏!单片机输出4种波形的函数信号发生器毕设(Proteus仿真+原理图+源码和论文)

西部超导材料科技股份有限公司

西部超导材料科技股份有限公司